ЮЂДІРэЦїНгПкаОЦЌЩшМЦЪЕР§

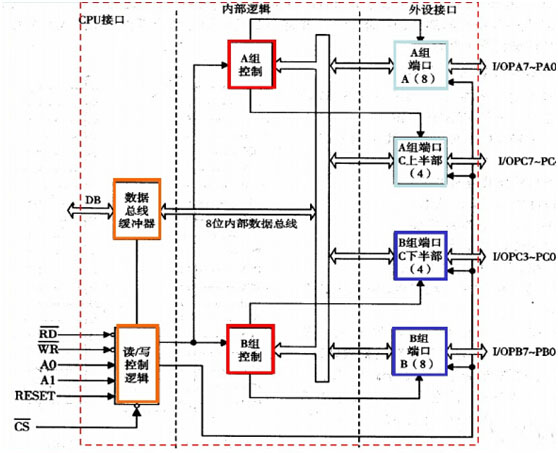

8255AПЩБрГЬВЂааЪфШыЁЂЪфГіНгПкаОЦЌЃЌЪЧБъзМЭтЮЇНгПкЕчТЗЁЃЫќВЩгУNMOSЙЄвежЦдьЃЌгУЕЅвЛ+5VЕчдДЙЉЕчЃЌефга40Ьѕв§НХЃЌВЩгУЫЋСажБЪжВхЪНЗтзАЁЃЫќгаAЁЂBЁЂCШ§ИіЖЫПкЙВ24ЬѕI/0ЯпЃЌПЩвдЭЈЙ§БрГЬЕФЗНЗЈРДЩшЖЈЖЫПкЕФИїжжI/0ЙІФмЁЃгЩгкЫќЙІФмЧПЃЌгжФмЗНБуЕигыИїжжЮЂЛњЯЕЭГЯрНгЃЌЖјЧвдкСЌНгЭтВПЩшБИЪБЃЌЭЈГЃВЛашвЊдйИНМгЭтВПЕчТЗЫљвдЕУЕНСЫЙуЗКЕФгІгУЁЃ

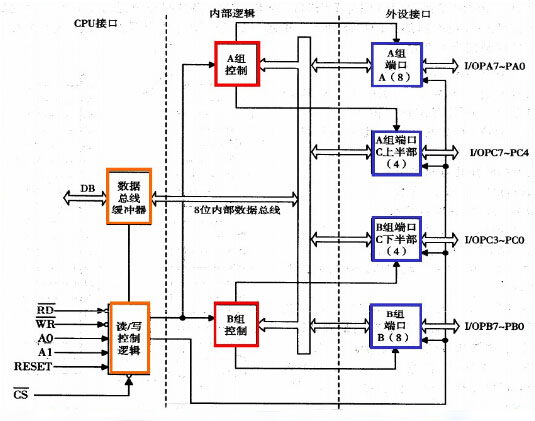

1ЁЂ8255AЕФФкВПНсЙЙгыв§НХ

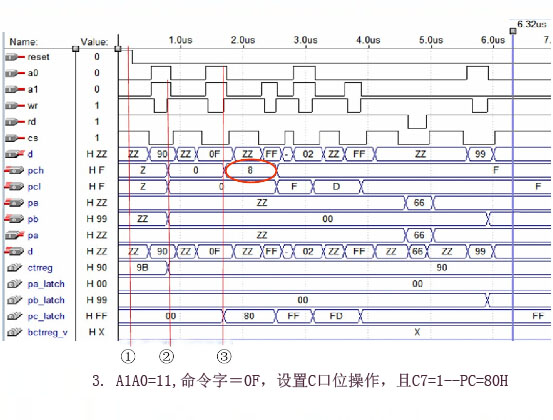

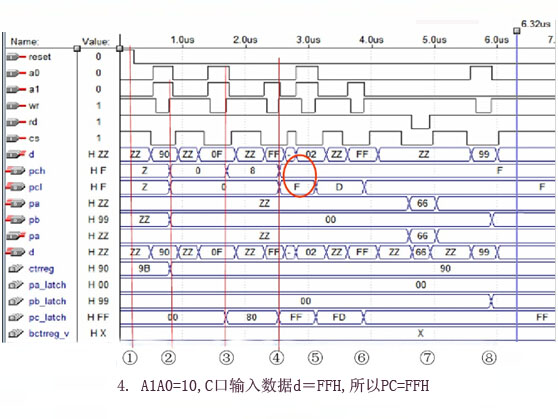

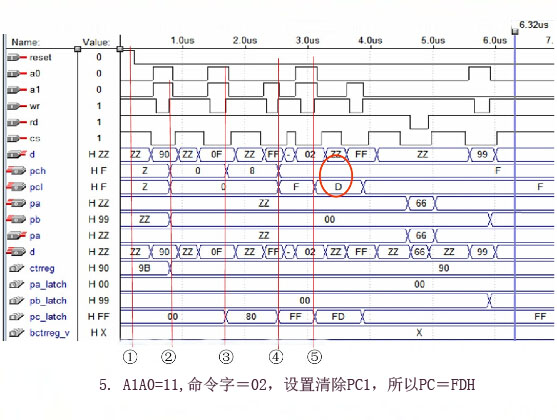

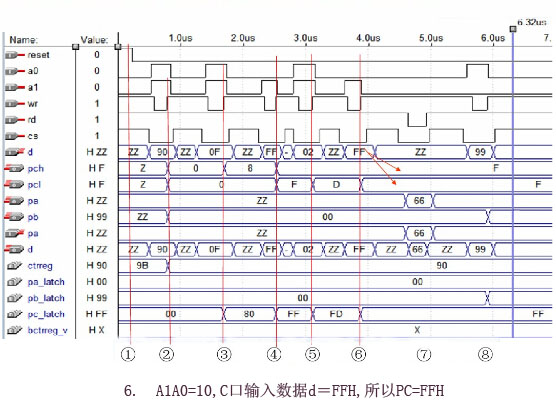

8255AЕФФкВПНсЙЙЭМ

1-1 8255AЕФФкВПНсЙЙ

ЃЈ1ЃЉ Ъ§ОнЖЫПкAЁЂBЁЂC

8255Aга3Иі8ЮЛЪ§ОнЖЫПкЃЌМДЖЫПкAЖЫПкBКЭЖЫПкCЁЃБрГЬШЫдБПЩвдЭЈЙ§ШэМўНЋЫќУЧЗжБ№зїЮЊЪфШыЖЫПкЛђЪфГіЖЫПкЃЌ3ИіЖЫПкдкВЛЭЌЕФЙЄзїЗНЪНЯТгаВЛЭЌЕФЙІФмНгМАЬиЕуЁЃ

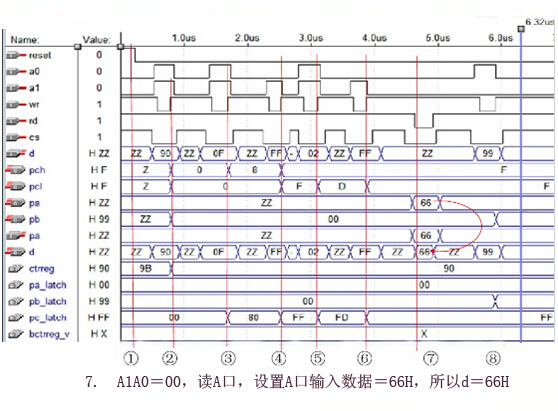

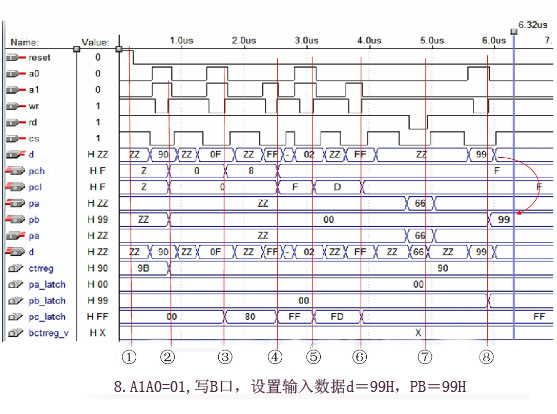

ЫЕУїЃК

1ЁЂ AПкгавЛИі8ЮЛЪ§ОнЪфГіЛКГхЁЂЫјДцЦїЃЌвЛИі8ЮЛЪ§ОнЪфШыЛКГхЁЂЫјДцЦїЁЃ

2ЁЂ BПкCПкгавЛИі8ЮЛЪ§ОнЪфГіЛКГхЁЂЫјДцЦїЁЂвЛИі8ЮЛЪ§ОнЪфШыЛКГхЦїЃЈЮоЫјДцЦїЃЉЁЃ

ЃЈ2ЃЉ AзщКЭBзщПижЦЕчТЗ

етЪЧСНзщИљОнCPUЕФУќСюзжПижЦ8255AЙЄзїЗНЪНЕФЕчТЗЁЃЫќУЧЕФПижЦМФДцЦїЯШНгЪмCPUЫЭГіЕФУќСюзжЃЌШЛКѓИљОнУќСюзжЗжБ№ОіЖЈСНзщЕФЙЄзїЗНЪНЃЌвВПЩИљОнCPUЕФУќСюзжЖдЖЫПкCЕФУП1ЮЛЪЕЯж АДЮЛ“ИДЮЛ”Лђ“жУЮЛ”ЁЃ

AзщПижЦЕчТЗПижЦЖЫПкAКЭЖЫПкCЕФЩЯАыВПЃЈPC7---PC4ЃЉЁЃ

BзщПижЦЕчТЗПижЦЖЫПкBКЭЖЫПкCЕФЯТАыВПЃЈPC3—PC0ЃЉЁЃ

(3)Ъ§ОнЛКГхЦї

етЪЧЫЋЯђ8ЮЛЛКГхЦїЃЌгУгкДЋЫЭMCS—51КЭ8255МфЕФПижЦзжЁЂзДЬЌзжКЭЪ§ОнзжЁЃ

ЃЈ3ЃЉ ЖСаДПижЦТпМ

ЃЈ4ЃЉ етВПЗжЕчТЗПЩвдНгЪеMCS—51ЫЭРДЕФЖСаДУќСюИїбЁПкЕижЗЃЌгУгкПижЦЖд8255AЕФЖСаДЁЃ

8255AЕФФкВПНсЙЙЭМ

1-2 8255AЕФаОЦЌв§НХ

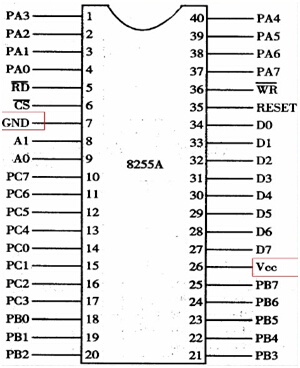

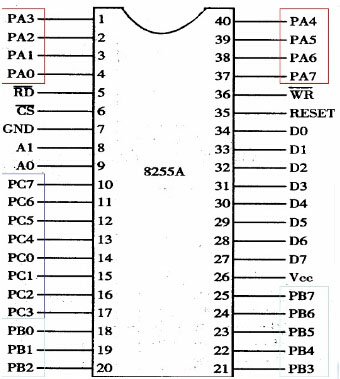

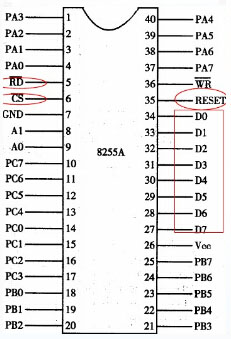

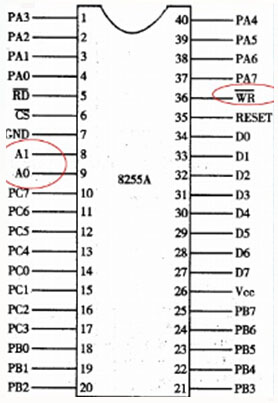

8255AЪЧвЛжжга40Иів§НХЕФЫЋСажБВхЪНБъзМаОЦЌЃЌЦфв§НХХХСаШчЭМЫљЪОЁЃГ§ЕчдДЃЈ+5VЃЉКЭЕивдЭтЃЌЦфЫќаХКХПЩвдЗжЮЊСНзщЁЃ

.ЃЈ1ЃЉгыЭтЩшЯрСЌНгЕФгаЃК

.PA7-PA0: AПкЪ§ОнЯп

.PB7-PB0: BПкЪ§ОнЯп

.PC7-PC0: CПкЪ§ОнЯп

ЃЈ2ЃЉгыCPUЯрСЌНгЕФгаЃК

D7-D0ЃК 8255AЕФЪ§ОнЯпЃЌКЭЯЕЭГЪ§ОнзмЯпЯрСЌЁЃ

RESETЃКИДЮЛаХКХЃЌИпЕчЦНгааЇЁЃЕБRESETгааЇЪБЃЌЫљгаФкВПМФДцЦїЖМБЛЧхГ§ЁЃЭЌЪБЃЌ3ИіЪ§ОнЖЫПкБЛздЖЏЩшЮЊЪфШыЗНЪНЁЃ

/CSЃК ЦЌбЁаХКХЃЌЕЭЕчЦНгааЇЁЃжЛгаЕБ/CSгааЇЪБЃЌаОЦЌВХБЛбЁжаЃЌдЪаэ8255AгыCPUНЛЛЛаХЯЂЁЃ

/RDЃКЖСаХКХЃЌЕЭЕчЦНгааЇЃЌЕБ/RDгааЇЪБЃЌCPUПЩвдДг8255AжаЖСШЁЪфШыЪ§ОнЁЃ

/WRЃКаДаХКХЃЌЕЭЕчЦНгааЇЁЃЕБ/WRгааЇЪБЃЌCPUПЩвдЭљ8255AжааДШыПижЦзжЛђЪ§ОнЁЃ

A1ЁЂA0ЃКЖЫПкбЁдёаХКХЃК

8255AФкВПга3ИіЪ§ОнЖЫПкКЭ1ИіПижЦЖЫПкЃЌЕБЃК

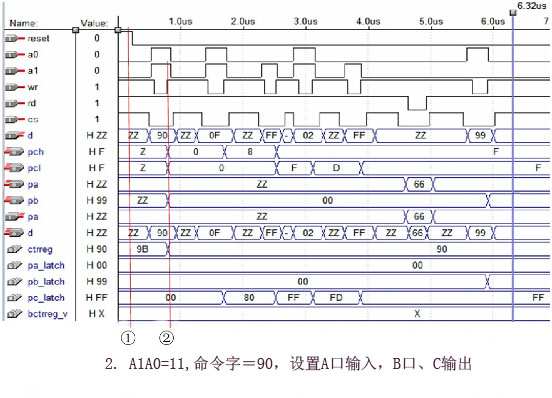

A1A0=00ЪБбЁжаЖЫПкAЃЛ

A1A0=01ЪБбЁжаЖЫПкBЃЛ

A1A0=10ЪБбЁжаЖЫПкCЃЛ

A1A0=11ЪБбЁжаПижЦПкЁЃ

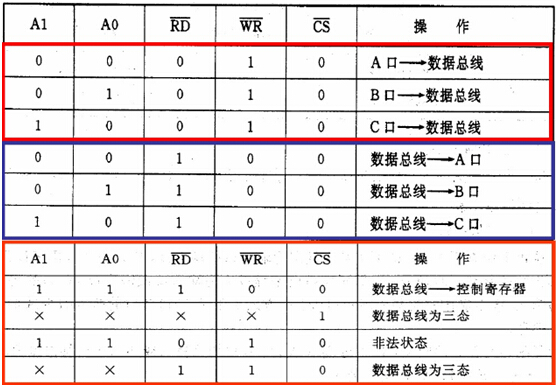

8255AЖЫПкбЁдёБэШчЯТЃК

1.3 8255AЕФПижЦзж

.8255AЮЊПЩБрГЬНгПкаОЦЌЃЌвдПижЦзжаЮЪНЪЅЦфЙЄзїЗНЪНКЭCПкИїЮЛЕФзДЬЌНјааЩшжУЁЃ

.гУЛЇПЩвдЭЈЙ§ГЬађПижЦзжЫЭЕН8255AЕФПижЦМФДцЦїЃЈA1A0=11ЃЉЁЃ

.гаСНжжПижЦзжЃКЙЄзїЗНЪНПижЦзжКЭCПкжУЮЛ/ИДЮЛПижЦзжЁЃвдПижЦзжЕФзюИпЮЛРДЧјЗжСНжжПижЦзжЁЃ

ЃЈ1ЃЉ ЙЄзїЗНЪНПижЦзж

8255AПижЦзжИёЪНЃКЙЄзїЗНЪНПижЦзж

ЙЄзїЗНЪНПижЦзжгУгкШЗЖЈИїПкЕФЙЄзї ЗНЪНМАЪ§ОнДЋЫЭЗНЯђ

ЫЕУїЃК

ЃЈ1ЃЉ Aзщга3жжЙЄзїЗНЪНЃЌЖјBзщжЛга2жжЙЄзїЗНЪНЁЃ

ЃЈ2ЃЉ AзщАќРЈAПкгыCПкЕФИп4ЮЛЃЈЩЯПкЃЉЃЌ

BзщАќРЈBПкгыCПкЕФЕЭ4ЮЛЃЈЯТПкЃЉЁЃ

ЃЈ3ЃЉ зюИпЮЛЃЈD7ЮЛЃЉЮЊБъжОЮЛЃЌ D7=1ЮЊЗНЪНПижЦзжЁЃ

ЗНЪН0ЃКЦеЭЈЪфШы/ЪфГіЗНЪНЁЃ ЃЈМђЕЅЕФI/OРЉеЙЃЉ

ЗНЪН1ЃКбЁЭЈЪфШы/ЪфГіЗНЪНЁЃ

ЗНЪН2ЃКAзщЫЋЯђЪфШы/ЪфГіЗНЪНЃЌBзщЮоЗНЪН2

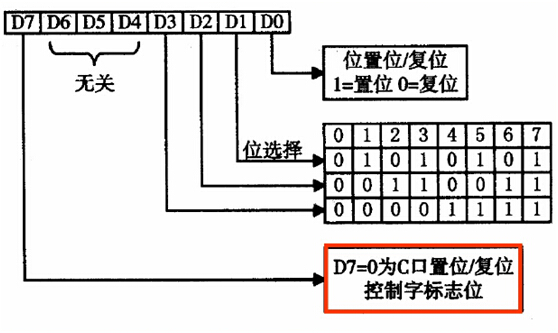

ЃЈ2ЃЉ CПкжУЮЛ/ИДЮЛПижЦзж

8255AПижЦзжИёЪНЃКCПкжУЮЛ/ИДЮЛПижЦзж

РћгУCПкжУЮЛ/ИДЮЛПижЦзжПЩвдКмЗНБуЕиЪЙCПк8ЮЛжаЕФШЮ вЛЮЛЧх0ЛђжУ1ЁЃ

ЫЕУїЃК

ЃЈ1ЃЉ дкЪЙгУжаЃЌИУПижЦзжУПДЮжЛФмЖдCПкжаЕФвЛЮЛНјаажУЮЛЛђИДЮЛЁЃ

ЃЈ2ЃЉ гІзЂвтЃЌдкЗНЪН1ЛђЗНЪН2ЪБЃЌCПкИїЮЛзїЮЊСЊТчЯпЪЙгУЃЌВЛФмВЩгУжУЮЛ/ИДЮЛРДВйзїЁЃЦфЪ§жЕгЩЭтНчвђЫиОіЖЈЁЃ

ЃЈ3ЃЉ D7ЮЛЮЊИУПижЦзжЕФБъжОЮЛЃЌD7=0ЮЊC ПкжУЮЛ/ИДЮЛПижЦзжЁЃ

1.4 8255ЕФЗНЪН0ЃЈЛљБОЪфШы/ЪфГіЗНЪНЃЉ

ВЛашвЊШЮКЮбЁЭЈаХКХЃЌAПкЁЂBПкМАCПкЕФИп4ЮЛИїЕЭ4ЮЛЖМПЩвдЩшЖЈЮЊЪфШыЛђЪфГіЁЃ

.зїЮЊЪфГіПкЪБЃЌЪфГіЕФЪ§ОнОљБЛЫјДцЃЛ

.зїЮЊЪфШыПкЪБЃЌAПкЕФЪ§ОнФмЫјДцЃЌBПкгыCПкЕФЪ§ОнВЛФмЫјДцЁЃ

.CПкОпгаАДЮЛИДЮЛгыжУЮЛЙІФмЁЃ

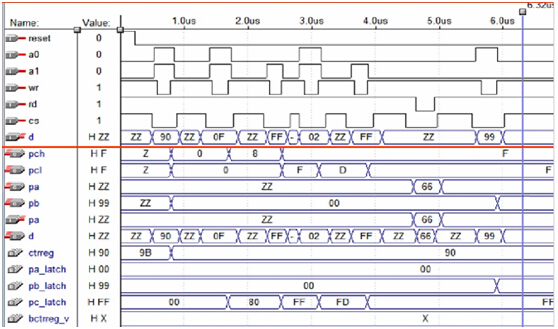

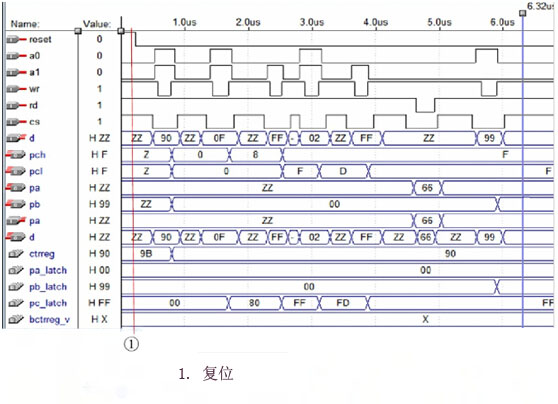

2 8255аОЦЌЕФVHDLУшЪі

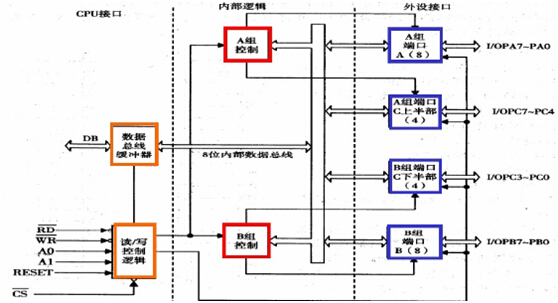

2.1 8255НсЙЙЩшМЦ

8255НсЙЙЩЯгЩШ§жжТпМЕчТЗЙЙГЩЃКЫјДцЦїЁЂзщКЯТпМЕчТЗКЭШ§ЬЌЛКГхЦїЁЃ

8255га7ИіЫјДцЦїЃК

Pa_latch---AПкЪфГіЫјДцЦїЃЌ8ЮЛЃЛ

Pb_latch---B ПкЪфГіЫјДцЦїЃЌ8ЮЛЃЛ

Pcl_latch---CПкЕЭ4ЮЛЪфГіЫјДцЦїЃЌ4ЮЛЃЛ

pch_latch---cПкИп4ЮЛЪфГіЫјДцЦїЃЌ4ЮЛЃЛ

8255га7ИіЫјДцЦїЃК

ctrreg---ЗНЪНПижЦзжМФДцЦїЃЌ8ЮЛЃЛ

bctrreg---CПкЮЛПижЦзжМФДцЦїЃЌ4ЮЛЃЛ

ctrregF---бЁдёБъжОМФДцЦїЃЌ1ЮЛЃЛ

=1Ъ§ОнДцШыЗНЪНПижЦМФДцЦїЃЌ

=0Ъ§ОнЕФЕЭ4ЮЛДцШыCПкПижЦзжМФДцЦїЁЃ

ЛКГхЦї

Ъ§ОнЯпD0-D7ЁЂЖЫПкPAЁЂPBЁЂPCЖМПЩвдЫЋЯђДЋЪфЪ§ОнЃЌвђДЫЃЌет4ИіЖЫПкгыЭтЕчТЗЯрСЌЪБЖМБиаыЪЧШ§ЬЌЕФЃЌетаЉв§НХЖМБиаыЪЧШ§ЬЌЫЋЯђв§НХЁЃ

зщКЯТпМЕчТЗ

жївЊгЩбЁдёЕчТЗКЭвыТыЕчТЗЙЙГЩЁЃ

2.2 8255аОЦЌЕФVHDLУшЪі

8255ЕФЙЄзїЙ§ГЬЃК

1ЁЂ аДПижЦзж

2ЁЂ ЖСЛђаДЪ§Он